AMD presented their portfolio of Adaptive SoC and FPGA solutions at the Embedded Tour in Massy, south of Paris.

Key takeaways

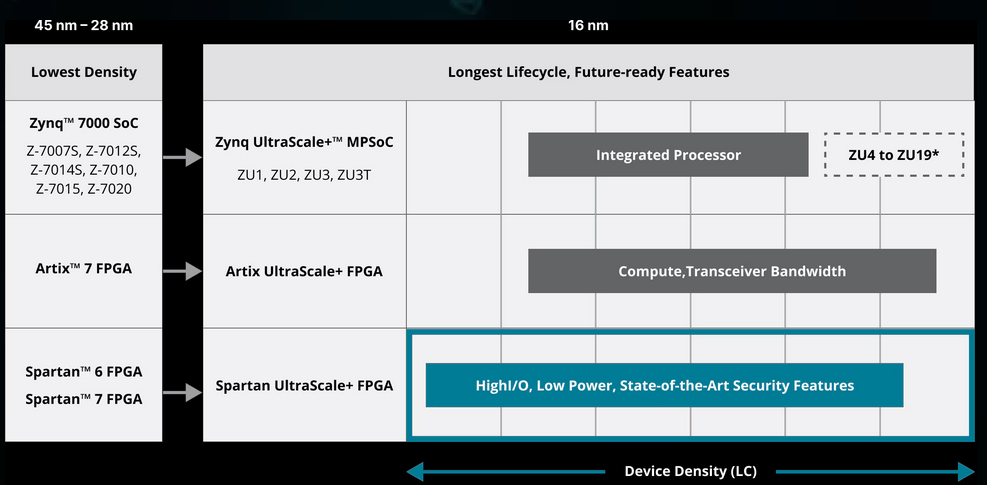

Cost-optimized portfolio: Zynq, Artix and Spartan cover the entry-level and mid-range segments. The UltraScale+ 16nm technology brings performance gains and power reduction compared to previous generations.

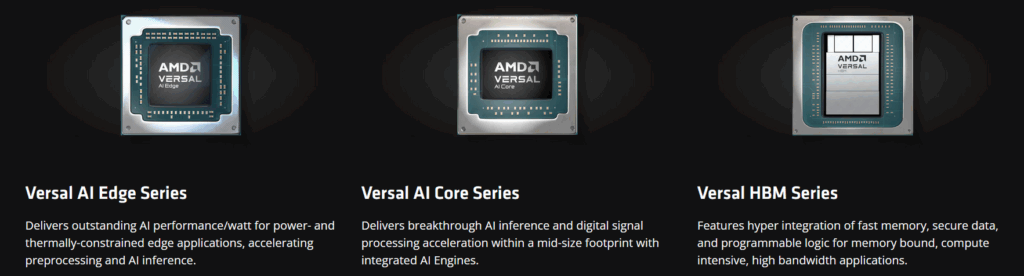

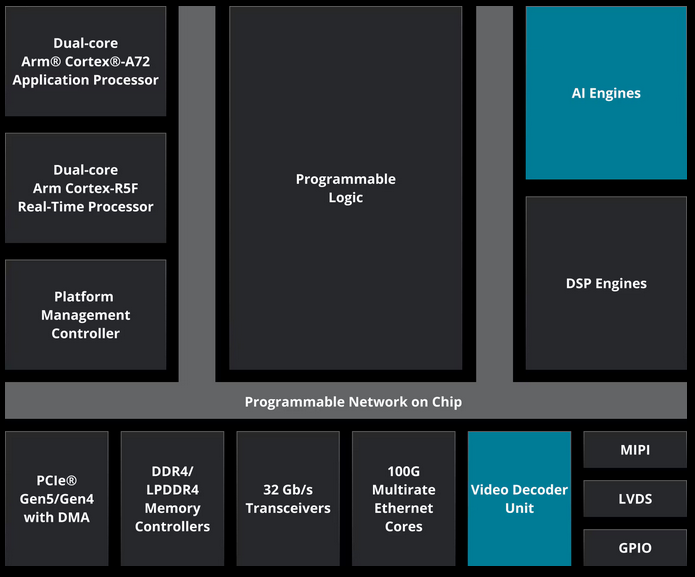

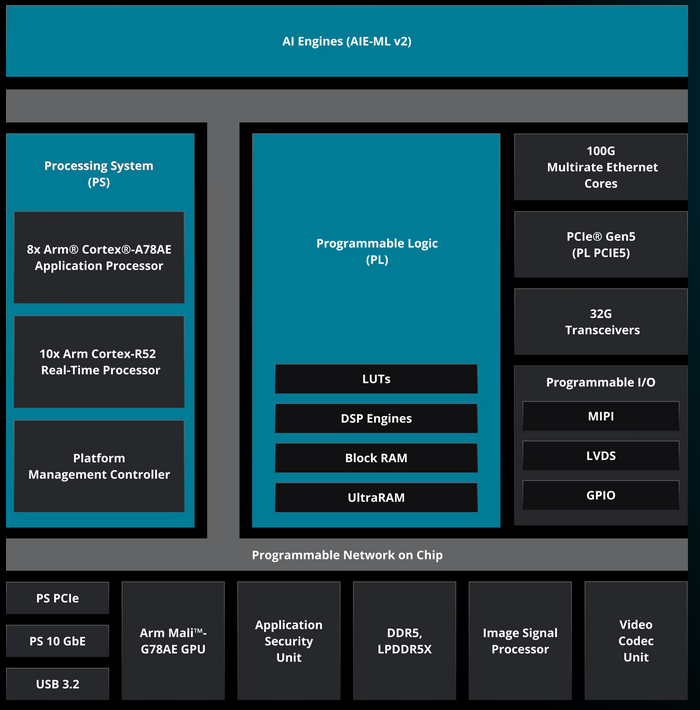

Versal Gen 2: an improved processing system with more CPUs and enhanced AI Engines (AIE). The architecture supports a clean pipeline from pre-processing (PL) to AI inference (AIE) to post-processing (PS).

Vitis IDE: AMD's unified development environment now integrates with PyTorch, TensorFlow and ONNX, making it easier to deploy trained models directly onto adaptive SoC platforms.

This event confirmed that the FPGA SoC ecosystem is maturing fast, with tooling and silicon that increasingly lower the barrier to entry for instrumentation teams.